USTC/LogicGates

From 2007.igem.org

(→NOT Gate) |

|||

| Line 52: | Line 52: | ||

[[Image:ustc_not gate.jpg|thumb]] | [[Image:ustc_not gate.jpg|thumb]] | ||

[[Image:ustc_not_truth table.jpg]] | [[Image:ustc_not_truth table.jpg]] | ||

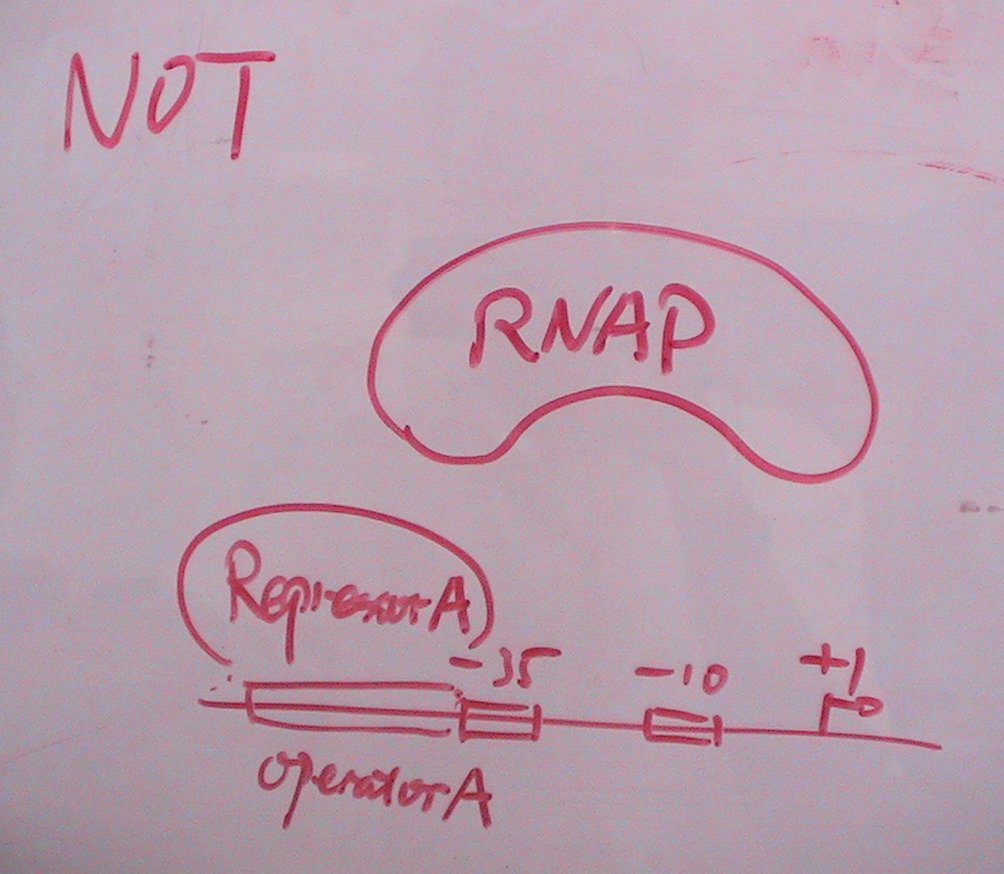

| - | The NOT gate | + | |

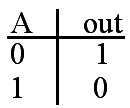

| - | (cited from wikipedia.com) | + | The NOT gate is a digital logic gate that implements logical negation. It behaves according to the truth table to the left. A HIGH output (1) results if the inputs is LOW (0). If the input is HIGH (1), a LOW output (0) results.(cited from wikipedia.com) |

| + | The draft to the right shows the NOT gate we design in the project. | ||

Revision as of 05:30, 2 August 2007

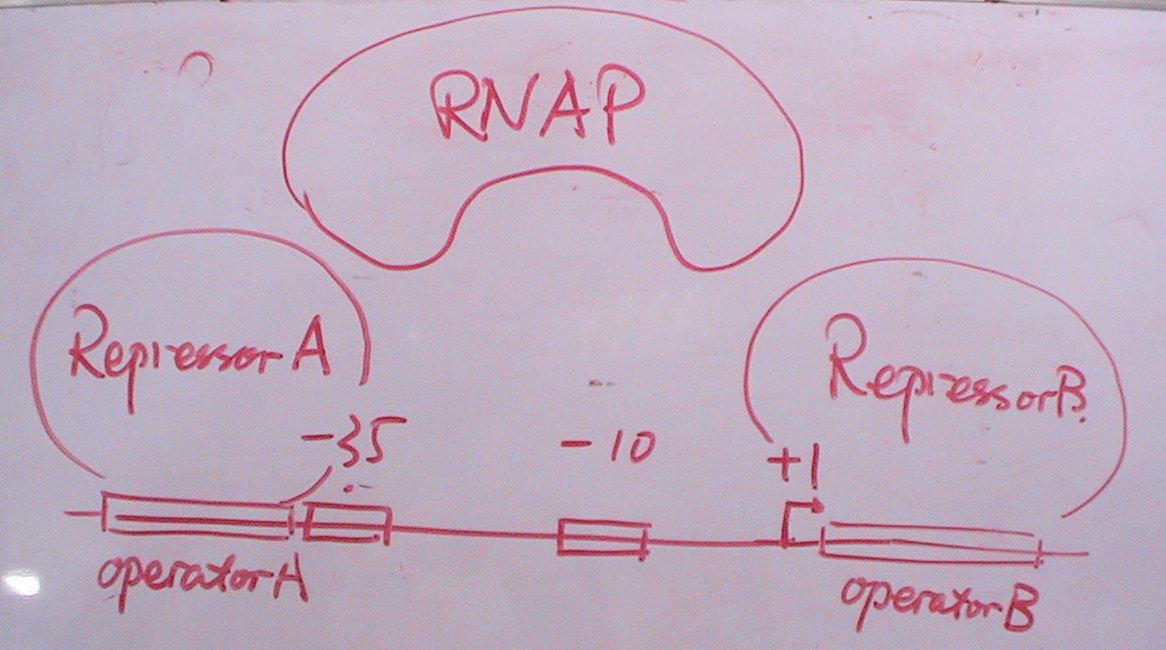

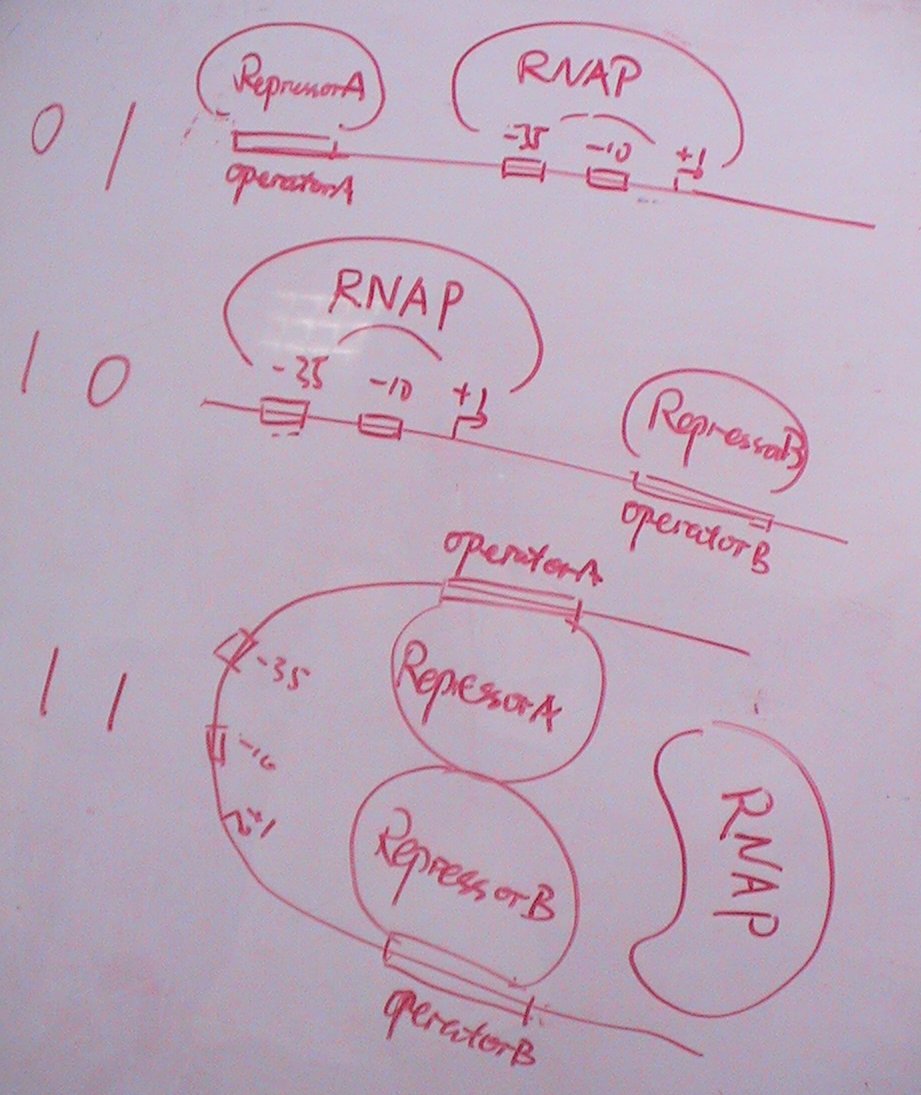

NOR Gate

The NOR gate is a digital logic gate that implements logical NOR - it behaves according to the truth table to the right. A HIGH output (1) results if both the inputs to the gate are LOW (0). If one or both input is HIGH (1), a LOW output (0) results.

p NOR q is only true when both p and q are false.

The NOR operation is a logical operation on two logical values, typically the values of two propositions, that produces a value of true if and only if both operands are false. In other words, it produces a value of false if and only if at least one operand is true.

NAND Gate

The NAND operation is a logical operation on two logical values, typically the values of two propositions, that produces a value of false if and only if both of its operands are true. In other words, it produces a value of true if and only if at least one of its operands is false.

The NAND operation is a logical operation on two logical values, typically the values of two propositions, that produces a value of false if and only if both of its operands are true. In other words, it produces a value of true if and only if at least one of its operands is false.

A LOW output results only if both the inputs to the gate are HIGH. If one or both inputs are LOW, a HIGH output results.

NOT Gate

The NOT gate is a digital logic gate that implements logical negation. It behaves according to the truth table to the left. A HIGH output (1) results if the inputs is LOW (0). If the input is HIGH (1), a LOW output (0) results.(cited from wikipedia.com) The draft to the right shows the NOT gate we design in the project.