USTC/LogicGates

From 2007.igem.org

m (→NOT Gate) |

m (→NOR Gate) |

||

| Line 6: | Line 6: | ||

The NOR gate is a digital logic gate that implements logical NOR - it behaves according to the truth table to the left. A HIGH output (1) results if both the inputs to the gate are LOW (0). If one or both input is HIGH (1), a LOW output (0) results. In other words, it produces a value of false if and only if at least one operand is true. (from wikipedia) | The NOR gate is a digital logic gate that implements logical NOR - it behaves according to the truth table to the left. A HIGH output (1) results if both the inputs to the gate are LOW (0). If one or both input is HIGH (1), a LOW output (0) results. In other words, it produces a value of false if and only if at least one operand is true. (from wikipedia) | ||

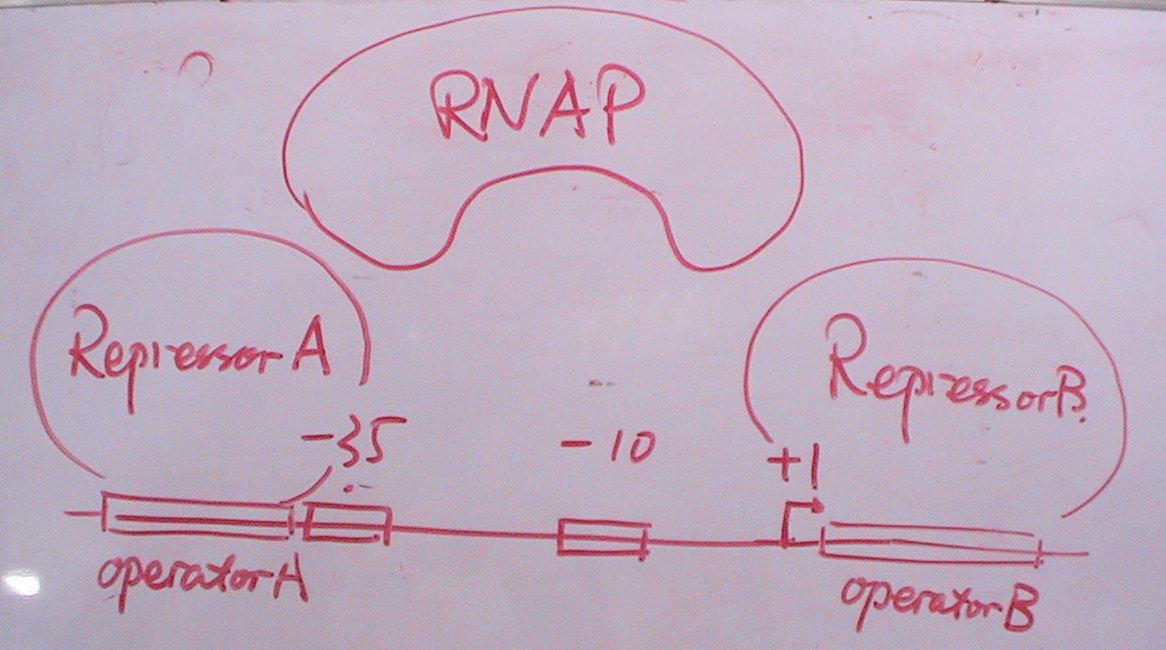

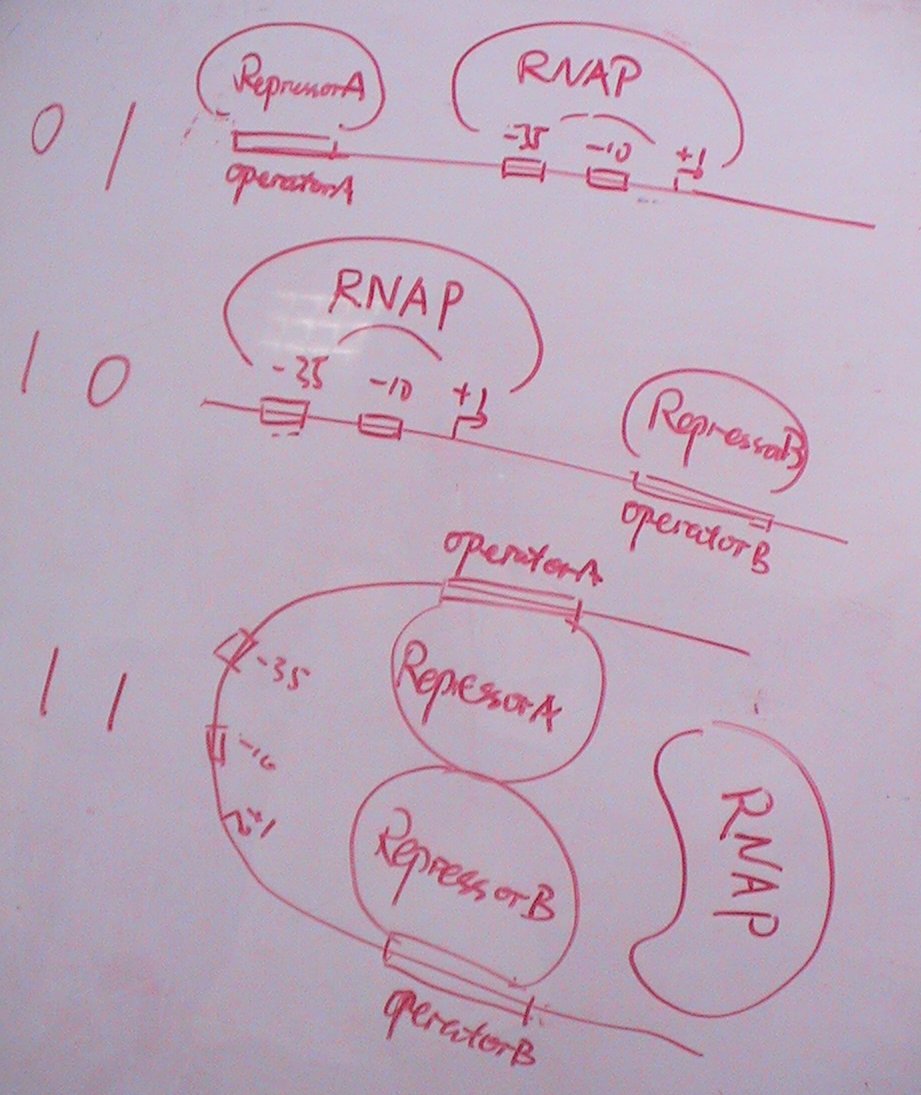

| - | The draft to the right shows the NOR Gate we have determined ourselves to experimentally implement. It is | + | The draft to the right shows the NOR Gate we have determined ourselves to experimentally implement. It is an extract made from our weekly group meeting. As is shown in the draft, the RNA Polymerase cannot bind to the its target site |

<TODO> | <TODO> | ||

Revision as of 03:03, 5 October 2007

NOR Gate

The NOR gate is a digital logic gate that implements logical NOR - it behaves according to the truth table to the left. A HIGH output (1) results if both the inputs to the gate are LOW (0). If one or both input is HIGH (1), a LOW output (0) results. In other words, it produces a value of false if and only if at least one operand is true. (from wikipedia)

The draft to the right shows the NOR Gate we have determined ourselves to experimentally implement. It is an extract made from our weekly group meeting. As is shown in the draft, the RNA Polymerase cannot bind to the its target site

<TODO>

NAND Gate

The NAND operation is a logical operation on two logical values, typically the values of two propositions, that produces a value of false if and only if both of its operands are true. In other words, it produces a value of true if and only if at least one of its operands is false. A LOW output results only if both the inputs to the gate are HIGH. If one or both inputs are LOW, a HIGH output results.(from wikipedia)

The draft to the right shows the NAND Gate we are destined to physically realize. It is also an extract made from an ordinary group meeting.

<TODO>

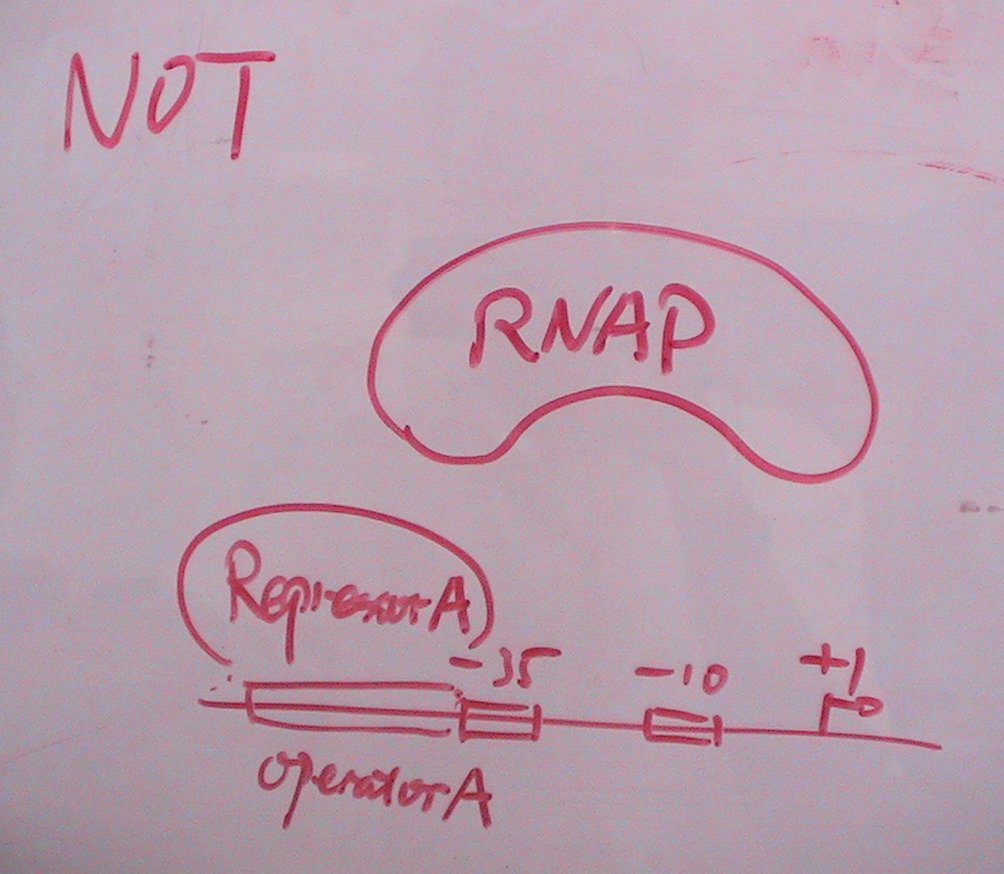

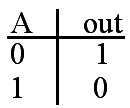

NOT Gate

The NOT gate is a digital logic gate that implements logical negation. It behaves according to the truth table to the left. A HIGH output (1) results if the inputs is LOW (0). If the input is HIGH (1), a LOW output (0) results. (from wikipedia)

The draft to the right shows the NOT gate we plan to complete in the project.

The existence of repressor A fulfils the function of a simple NOT Gate. RNA Polymerase will not bind to the according RBS when the repressor has already bounds an operator. Not until the operator is relieved from the repressor will the RNA Polymerase come to work again.