USTC/Demonstration

From 2007.igem.org

(Difference between revisions)

m |

m |

||

| Line 5: | Line 5: | ||

* includes all the three logic gates, which form into a three-level logic circuit; | * includes all the three logic gates, which form into a three-level logic circuit; | ||

* shows that wires can cross and branch off (without interference); | * shows that wires can cross and branch off (without interference); | ||

| - | * is loaded on two plasmids, [http://partsregistry.org/Part:BBa_I732998 pSB1A3-I732998] and [http://partsregistry.org/Part:BBa_I732999 pSB1A3-I732999] , | + | * is loaded on two plasmids, [http://partsregistry.org/Part:BBa_I732998 pSB1A3-I732998] and [http://partsregistry.org/Part:BBa_I732999 pSB1A3-I732999] ,and transformed into Top10 strain in practice; |

| - | and transformed into Top10 strain in practice; | + | |

* accepts aTc and AHL signals as inputs; | * accepts aTc and AHL signals as inputs; | ||

Revision as of 18:52, 21 October 2007

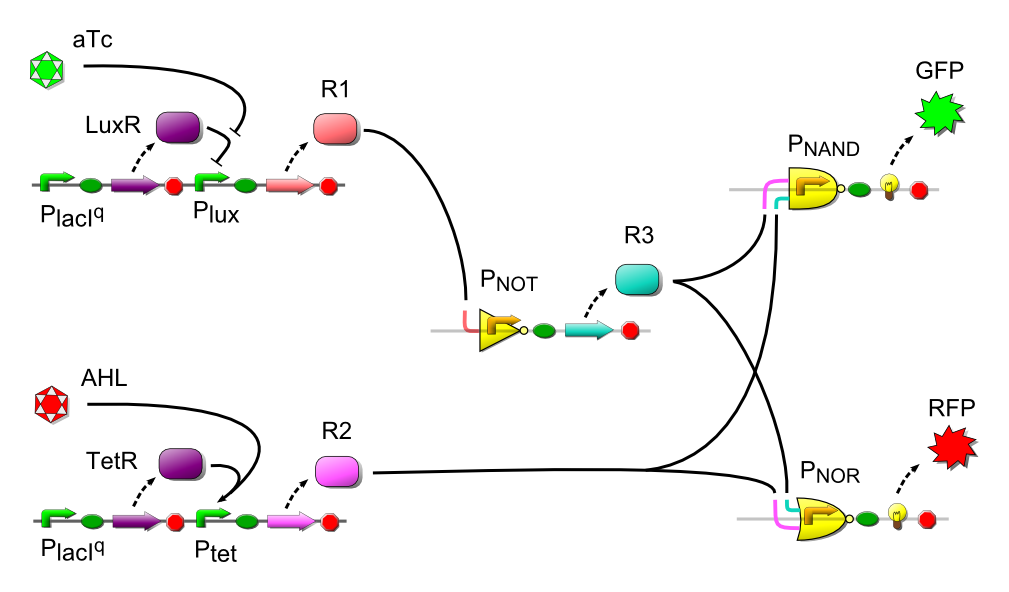

An actual demonstration is decided to show the extensible ability of our method.

This demo system

- is designed as simple as possible, without no "cool" logic function;

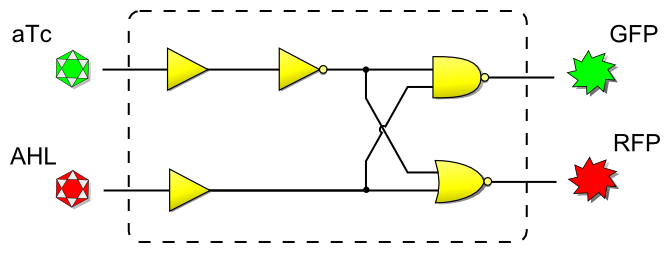

- includes all the three logic gates, which form into a three-level logic circuit;

- shows that wires can cross and branch off (without interference);

- is loaded on two plasmids, [http://partsregistry.org/Part:BBa_I732998 pSB1A3-I732998] and [http://partsregistry.org/Part:BBa_I732999 pSB1A3-I732999] ,and transformed into Top10 strain in practice;

- accepts aTc and AHL signals as inputs;

- produces RFP and GFP signals as outputs;

- can be "resetted" by IPTG signal (i.e. all outputs lighten when IPTG added in);

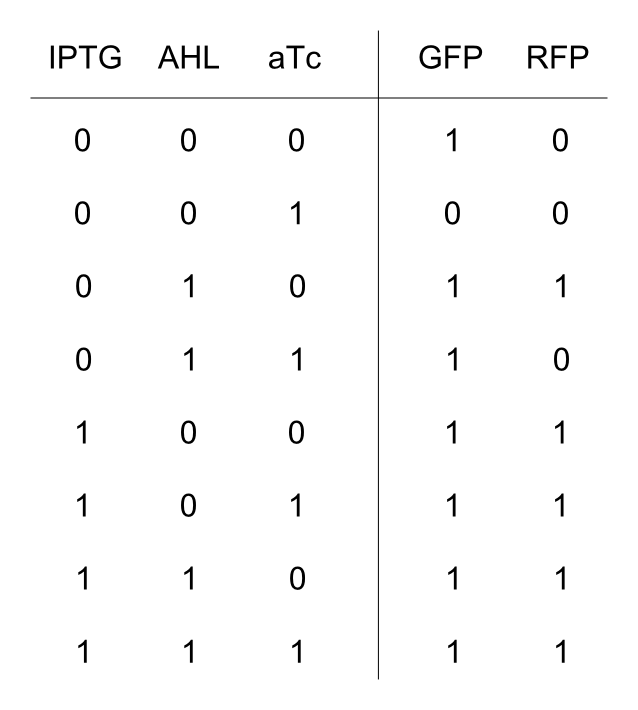

- is expected to output the results as the truth table shown in Figure 2.