USTC/Demonstration

From 2007.igem.org

(Difference between revisions)

m |

m |

||

| Line 1: | Line 1: | ||

| - | [[Image: | + | A actual demonstration shown in Figure 1 is decided to be built up to show the ability |

| - | [[Image: | + | of our method. This demo system is designed as simple as possible, without no "cool" logic |

| - | [[Image:DemonstrationTruthTable.png|thumb]] | + | function. But all the three logic gates are included, form into a three-level logic circuit. Meanwhile wires can cross and branch off. Figure 2 shows the signal pathway, and all the components |

| + | are loaded on plasmid [http://partsregistry.org/Part:BBa_I732998 pSB1A3-I732998] and [http://partsregistry.org/Part:BBa_I732999 pSB1A3-I732999]. | ||

| + | |||

| + | This demo system accepts aTc and AHL signal, and is expected to output the results as the truth table shown in Figure 3. | ||

| + | |||

| + | [[Image:DemonstrationLogic.png|thumb|512px|left|'''Figure 1''']] | ||

| + | |||

| + | [[Image:DemonstrationSystem.png|thumb|512px|'''Figure 2''']] | ||

| + | |||

| + | [[Image:DemonstrationTruthTable.png|thumb|'''Figure 3''']] | ||

Revision as of 15:56, 16 October 2007

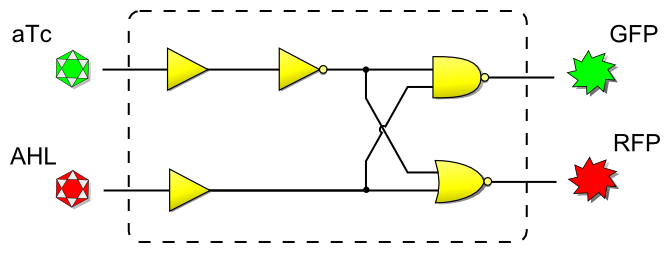

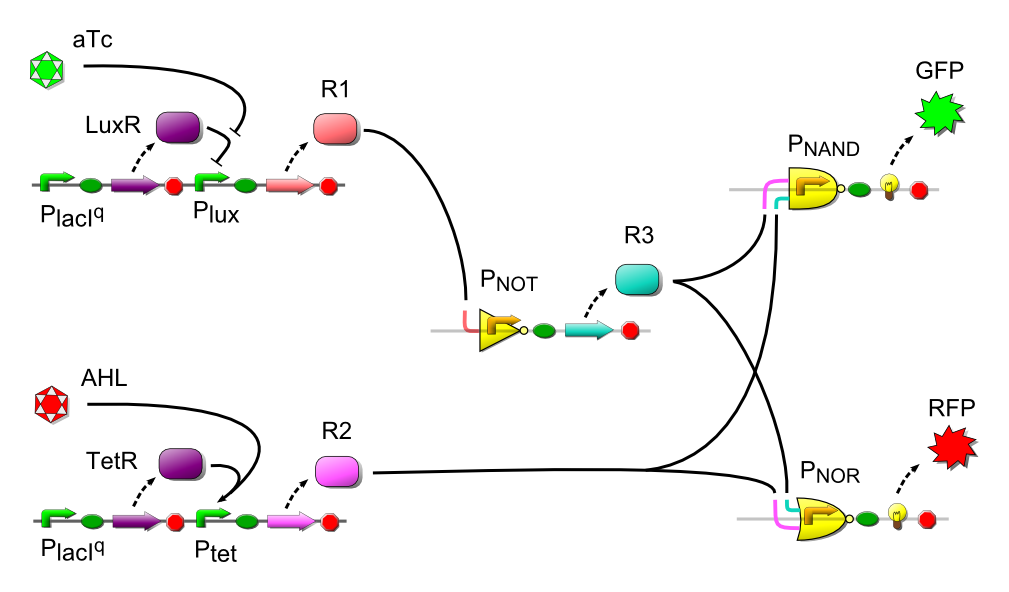

A actual demonstration shown in Figure 1 is decided to be built up to show the ability of our method. This demo system is designed as simple as possible, without no "cool" logic function. But all the three logic gates are included, form into a three-level logic circuit. Meanwhile wires can cross and branch off. Figure 2 shows the signal pathway, and all the components are loaded on plasmid pSB1A3-I732998 and pSB1A3-I732999.

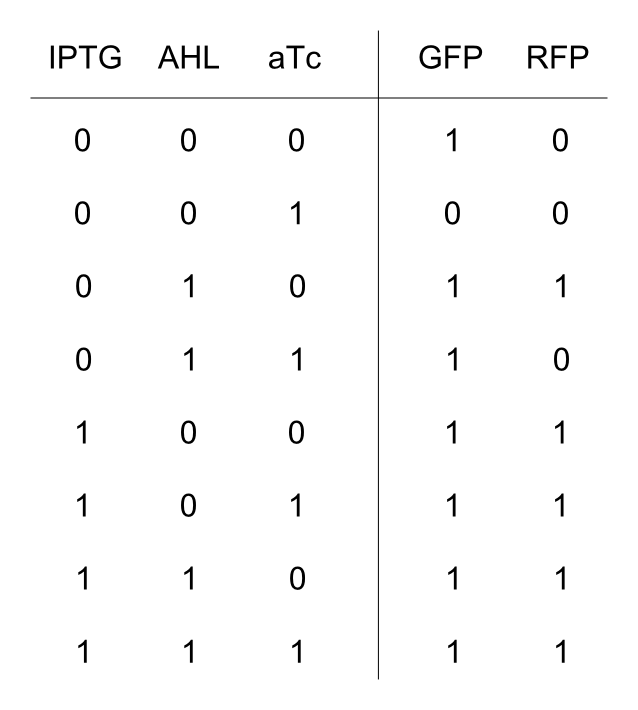

This demo system accepts aTc and AHL signal, and is expected to output the results as the truth table shown in Figure 3.