Tianjin/FLIP-FLOP

From 2007.igem.org

Sunlovedie (Talk | contribs) |

Sunlovedie (Talk | contribs) |

||

| Line 30: | Line 30: | ||

<br> | <br> | ||

<font size="3" color="#0000CC">2.1<font>[[Tianjin/FLIP-FLOP/Model2|<font size="3" color="#0000CC">Change the degradation speed of AHL</font>]] | <font size="3" color="#0000CC">2.1<font>[[Tianjin/FLIP-FLOP/Model2|<font size="3" color="#0000CC">Change the degradation speed of AHL</font>]] | ||

| + | <br> | ||

| + | <font size="3" color="#0000CC">2.1<font>[[Tianjin/FLIP-FLOP/Model2|<font size="3" color="#0000CC">parameter sensitivity</font>]] | ||

|- | |- | ||

|width="960px" style="padding: 10px; background-color: #00CC00" | | |width="960px" style="padding: 10px; background-color: #00CC00" | | ||

Revision as of 12:19, 25 October 2007

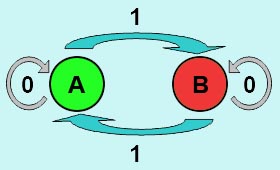

Design"Flip-flop" is the common name given to two-state devices which offer basic memory for sequential logic operations. Flip-flops are widely used for digital data storage and transfer as well as in banks called "registers" for the storage of binary numerical data. Based on the conception of "Flip-flop" and synthetic biology, we designed the Genetically RS FLIP-FLOP whose output signal is regulated by additional input signal. Besides this, we modulate the performance of Genetically RS FLIP-FLOP to optimize our original design. 1.Introduction to the logic rules of our flip-flop

|

Modeling1.Construction of Mathematical Model 2.Model Result

|

Experiment |